Electronic Devices and Circuits: Unit II: Amplifiers

Biasing the MOSFET

The self bias technique given for JFET cannot be used for establishing an operating point for the enhancement MOSFET because of the voltage drop across RS is in a direction to reverse bias the gate and it actually needs forward gate bias.

BIASING THE MOSFET

Biasing of Enhancement MOSFET

Fig.

2.11 shows the drain-to-gate bias circuit for enhancement mode MOSFET.

Here

the gate bias voltage is  This circuit offers the dc stabilization

through the feedback resistor Rf. However, the input resistance is

reduced because of Miller effect.

This circuit offers the dc stabilization

through the feedback resistor Rf. However, the input resistance is

reduced because of Miller effect.

Also

the voltage divider biasing technique given for JFET can be used for the

enhancement MOSFET. Here, the dc stability is accomplished by the de feedback

through RS.

But

the self bias technique given for JFET cannot be used for establishing an

operating point for the enhancement MOSFET because of the voltage drop across RS

is in a direction to reverse bias the gate and it actually needs forward gate

bias.

Fig.

2.12 shows an N- channel enhancement mode MOSFET common source circuit with

source resistor. The gate voltage is

and

the gate to source voltage is

VGS = VDD - VG

Assuming

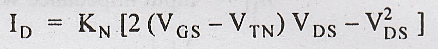

that VGS > VTN and the MOSFET is biased in the

saturation region, the drain current is

Here

the threshold voltage VTN and conduction parameter KN are

functions of temperature.

The

drain to source voltage is

VDS

= VDD – ID RD

If

VDS > VDS (sat) = VGS – VTN,

then the MOSFET is biased in the saturation region. If VDS < VDS

(sat) = VGS – VTN, then the MOSFET is biased in the

non saturation region, and the drain current is given by

Biasing Depletion MOSFET

Both

the self-bias technique and voltage divider bias circuit given for JFET can be

used to establish an operating point for the depletion mode MOSFET.

Electronic Devices and Circuits: Unit II: Amplifiers : Tag: : - Biasing the MOSFET

Related Topics

Related Subjects

Electronic Devices and Circuits

EC3353 - EDC - 3rd Semester - ECE Dept - 2021 Regulation | 3rd Semester ECE Dept 2021 Regulation